# De la modélisation au prototypage rapide

Environnement LabVIEW

Matériel compactRIO

Jean-Philippe BRAUD Société Phalanx

Alliance

Partner

Phalanx

La compétence à votre côté

# Sommaire

- **Présentation des outils de simulation sous LabVIEW**

- Simulation module

- Démonstration sous LabVIEW

- **Validation d'un algorithme en prototypage rapide**

- Introduction au système de test : Compact RIO

- Etude de cas réel

- Apport du prototypage rapide d'algorithme

- **Questions/Réponses**

# L'intervenant

Fondateur de Phalanx le 1<sup>er</sup> avril 2011.

Développeur certifié depuis 2007.

Architecte certifié LabVIEW depuis 2013.

Développe et supervise la réalisation de bancs de test, Acquisition de données

Réalisation d'IHM, de contrôle-commande embarqués

Utilisation majoritaire de LabVIEW

Intégration de code Matlab sous LabVIEW

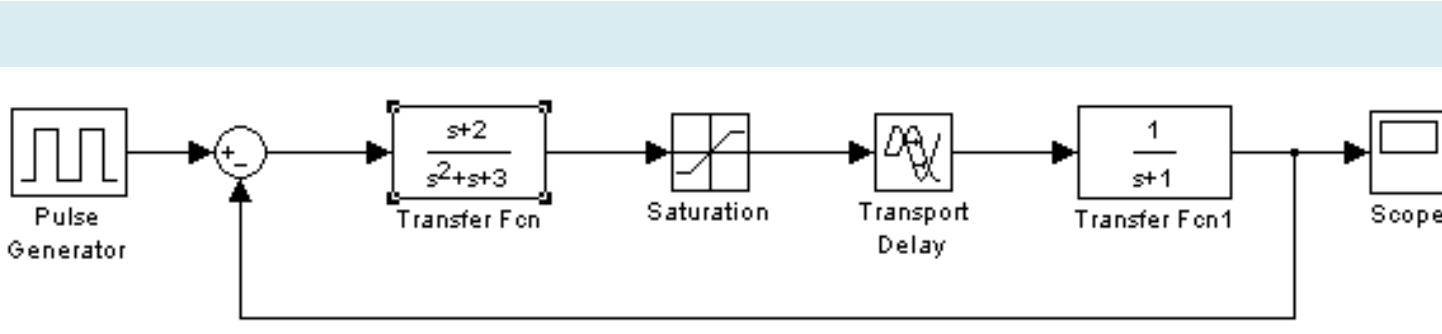

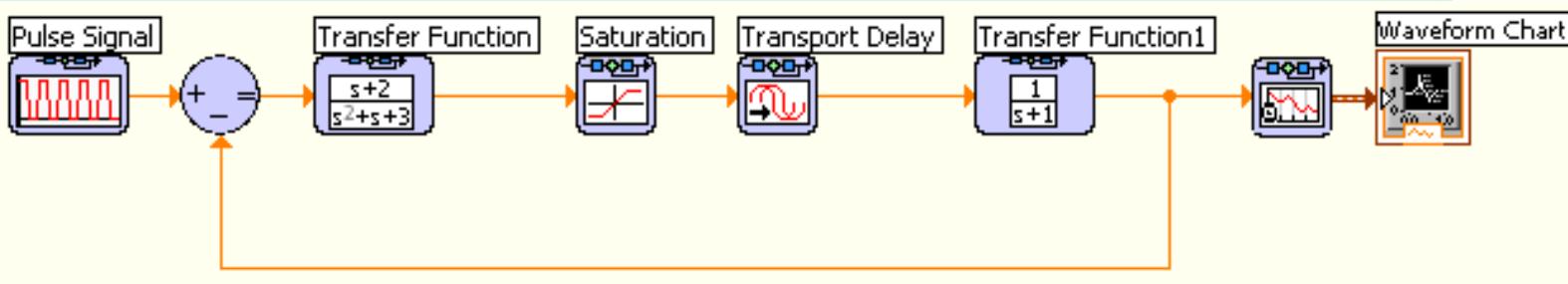

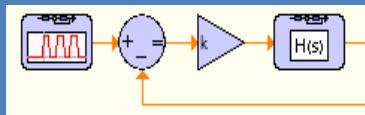

# Simulation module

## ■ Un environnement connu

# Simulation module

## ■ Ses fonctionnalités

Systèmes linéaires continus et discrets

Système non-linéaires

Par pas fixes, variables

Linéarisation

Visualisation 3D

# Deploy to Hardware Through LabVIEW

The MathWorks Inc.

software development

environment

MathScript RT

Module

Your .m code

MATLAB®

Control Design &

Simulation Module

Your .mdl code

Simulink®

Simulink Coder™

LabVIEW Real-Time

NI VeriStand

# Simulation module

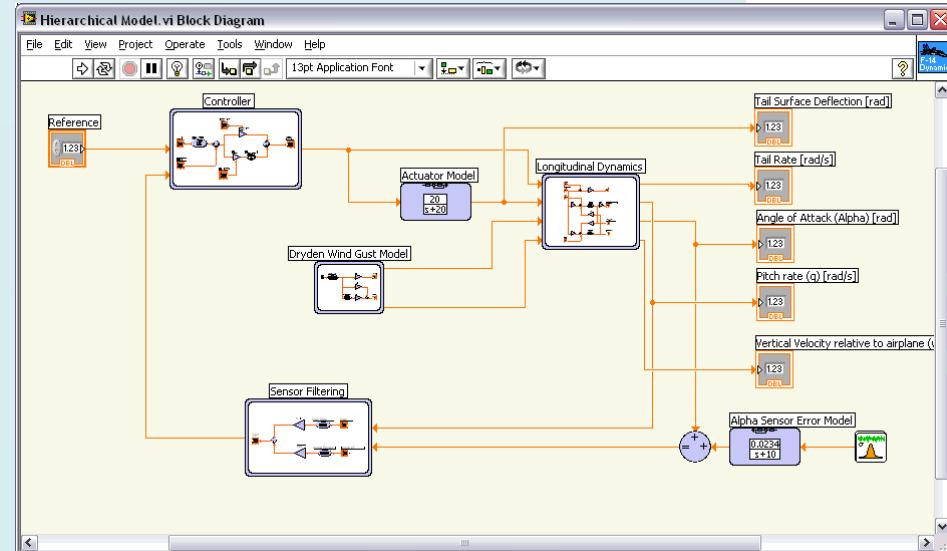

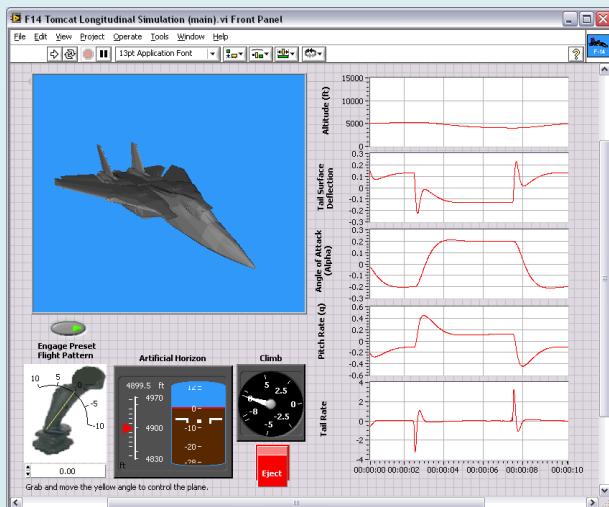

## Utilisation

Simulation de système dynamique

Implémentation temps réel pour du prototypage rapide ou Hardware In the Loop.

(HIL)

## Démonstration sous LabVIEW

# Validation d'un algorithme en prototypage rapide

Matériel RIO

Exemple d'utilisation

# Matériel RIO

## ■ Un cœur en RT et un accès FPGA

# Exemple d'utilisation

## ■ Validation d'un algorithme en prototypage rapide

Besoin : Rétrofit et modernisation d'un banc Aéro.

Problème : Algorithme existant mal compris et demande client exigeante.

- 1 – Analyse du besoin

- 2 – Utilisation sous Real Time de l'algorithme de contrôle.

- 3 – Implémentation sous RT et FPGA.

# 1 – Analyse du besoin

```

void CreateRectRgn(80,160,80+RectSizeX,y0c+RectSizeY)

gn_PtInRegion(point)

double x0c,y0c;

for(int i=0;i<NUMCITY;i++)

{

x0c=80+RectSizeX*(x0c+RectSizeX);

y0c=160+RectSizeY*(y0c+RectSizeY);

CreateEllipticRgn(x0c,y0c,RectSizeX,RectSizeY);

}

```

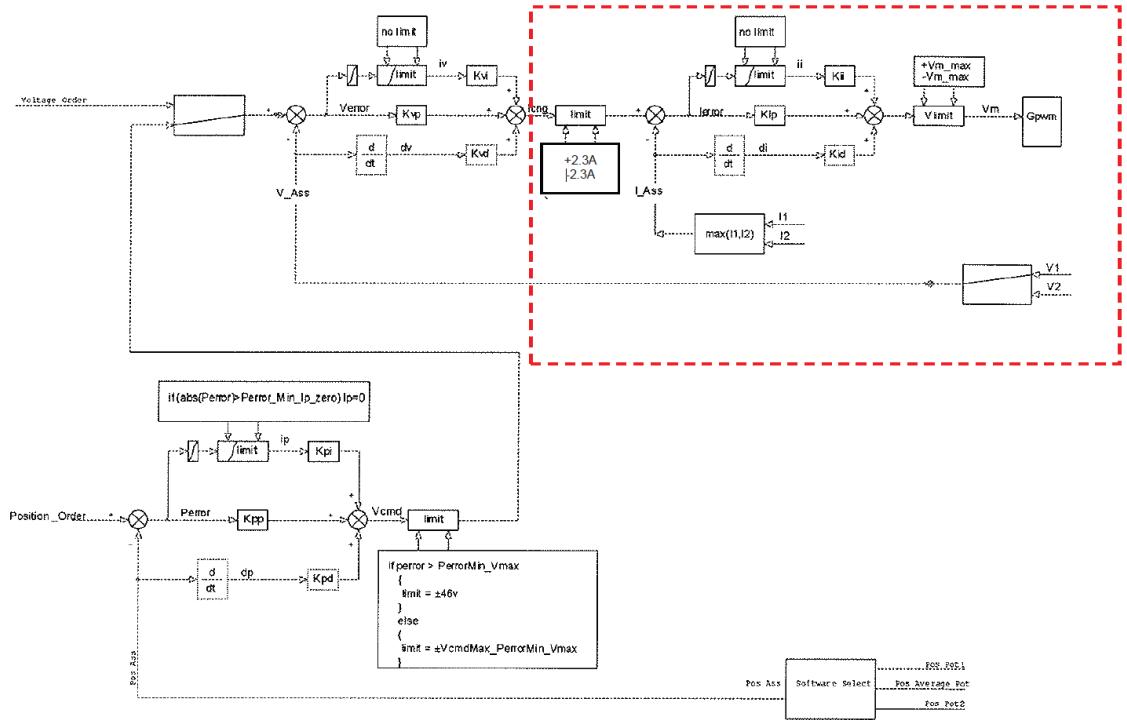

## Existant :

- 3 boucles PID en cascade

- position, courant, tension

- Régulation à 100Hz (10ms)

## Nouveau banc :

- Kis, Kps et Kds inconnus

- Trois vitesses distinctes

- 100Hz, 1kHz, 10kHz

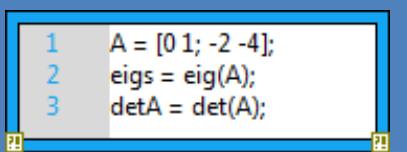

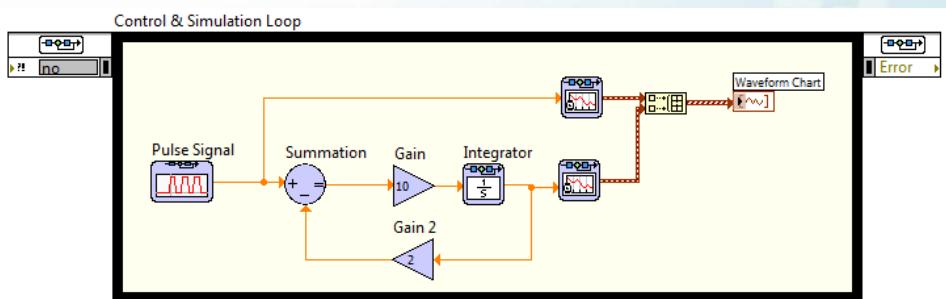

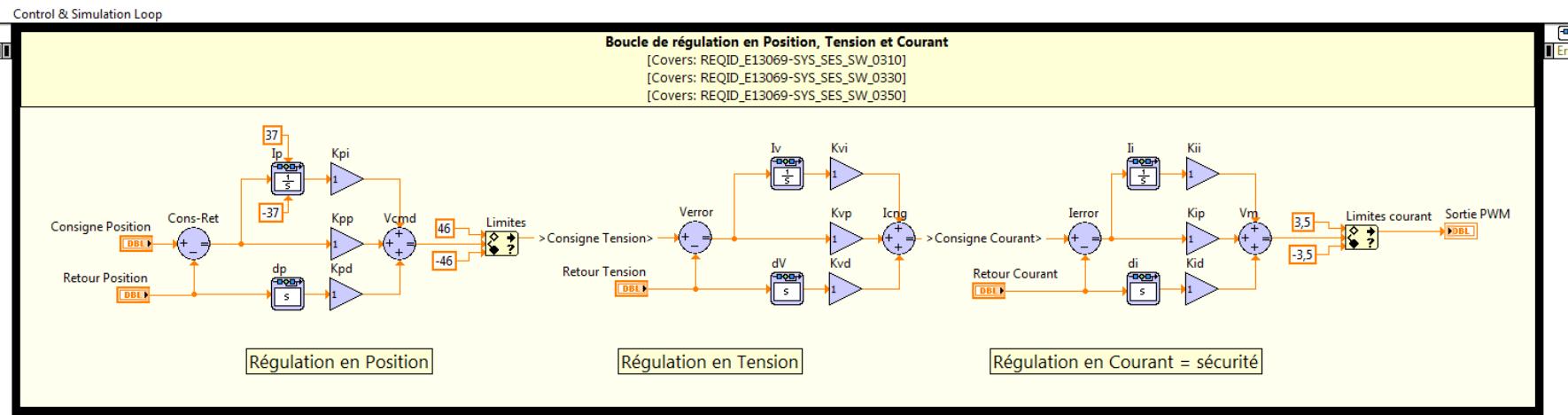

# 2 – Algorithme en Temps Réel

Passage de l'algorithme « brut » sous LabVIEW avec le module Simulation.

Tester l'idée et estimer les gains.

100Hz (10ms)

Moteur d'idées pour véhicules spécifiques et mobilité durable

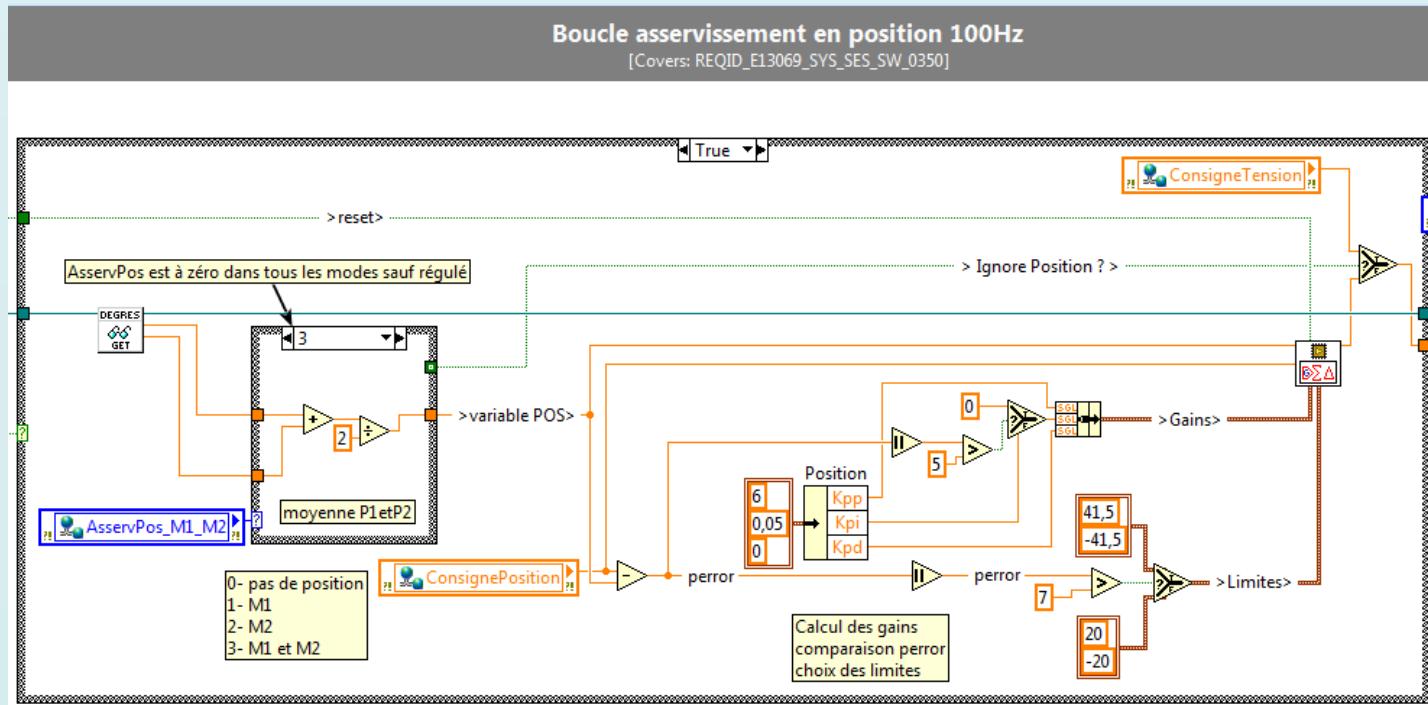

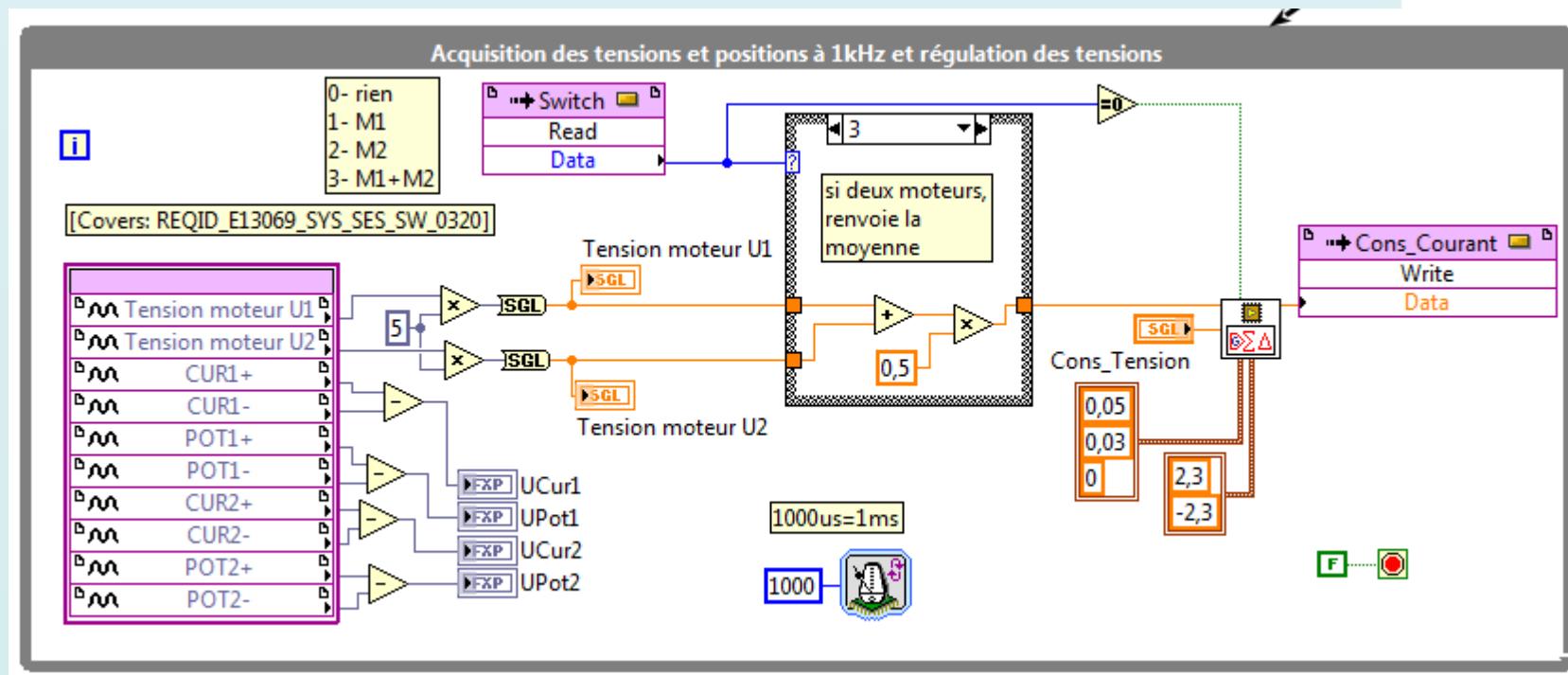

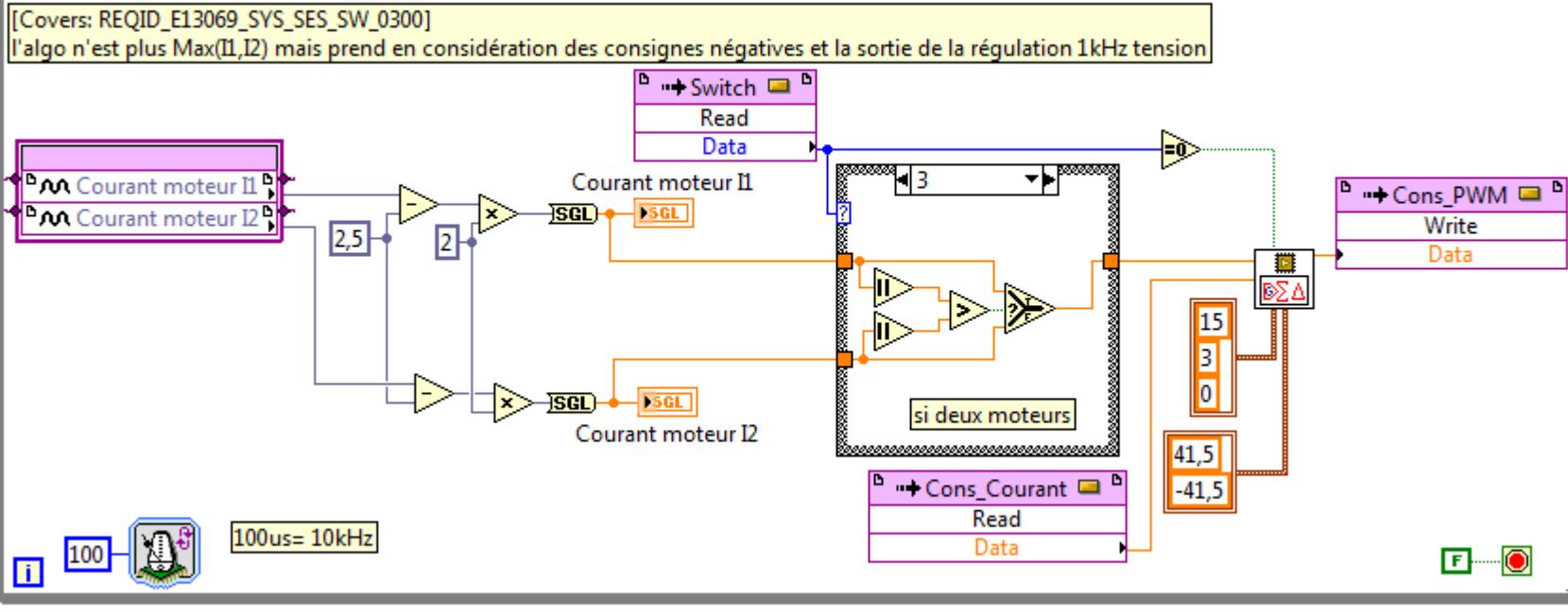

# 3 – Implémentation sous RT et FPGA

## Répartition des boucles :

- 100Hz sous RT pour limiter la charge sous FPGA,

- 1kHz sur le FPGA pour respecter les cadencements,

- 10KHz sur le FPGA.

## Prise sur le FPGA :

- 2 PWM,

- 2 PID,

- acquisitions de données,

- multiplexage,

- sécurités,

- Watchdog,

- =>96% du FPGA utilisé !!!

# 3 – Implémentation sous RT et FPGA

28/11/2014

# 3 – Implémentation sous RT et FPGA

```

void CreateRectRgn(80,160,80+

jn, PtInRegion(point))

double xOc,yOc;

for(int i=0;i<NUMCITY;i++)

xOc=80+RectSizeX*(i*xs)

yOc=160+RectSizeY*(i*ys)

rgnEllipse->CreateRegion(

```

Moteur d'idées pour véhicules spécifiques et mobilité durable

# 3 – Implémentation sous RT et FPGA

## Acquisition et régulation des courants à 10kHz

Moteur d'idées pour véhicules spécifiques et mobilité durable

# Apport du prototypage rapide

## Gain de temps sur l'intégration du logiciel :

- Validation d'un algorithme, des limites d'un système, des IHMs et transfert des données.

## Gain de temps matériel:

- Validation de la mécanique

- Validation de l'électronique

- Le tout en système dégradé

On limite donc l'impact de l'intégration logicielle finale sur le projet global et les dépassements associés.

# Mot de la fin ?

Aujourd’hui on demande aux ingénieurs et techniciens de faire vite et bien au moindre coût... **Ces objectifs sont juste ridicules !**

Mais il faut les tenir au mieux.

Aussi, prototyper et réaliser des intégrations intermédiaires apparaît comme la bonne méthode.

[www.captronic.fr](http://www.captronic.fr)

Moteur d'idées pour véhicules spécifiques et mobilité durable

JESSICA FRANCE - 17, rue des Martyrs - 38054 GRENOBLE

Cedex 09

CAP'TRONIC, un programme financé par :

JESSICA FRANCE fondée par :

direction générale de la compétitivité

de l'industrie et des services